Product Summary

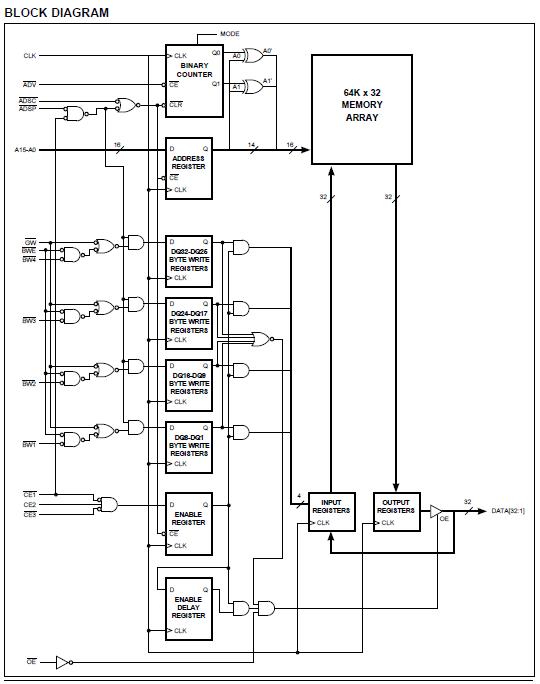

The ICSI IS61LV6432-6TQ is a high-speed, low-power synchronous static RAM designed to provide a burstable, high-performance, secondary cache for the Pentium, 680X0, and PowerPC microprocessors. The IS61LV6432-6TQ is organized as 65,536 words by 32 bits, fabricated with ICSI’s advanced CMOS technology. The IS61LV6432-6TQ integrates a 2-bit burst counter, high-speed SRAM core, and high-drive capability outputs into a single monolithic circuit. All synchronous inputs pass through registers controlled by a positive-edge-triggered single clock input.

Parametrics

IS61LV6432-6TQ absolute maximum ratings: (1)Temperature Under Bias: –10 to +85 ℃; (2)TSTG Storage Temperature: –55 to +150 ℃; (3)PD Power Dissipation: 1.8 W; (4)IOUT Output Current (per I/O): 100 mA; (5)VIN, VOUT Voltage Relative to GND for I/O Pins: –0.5 to VCCQ + 0.3 V; (6)VIN Voltage Relative to GND for for Address and Control Inputs: –0.5 to 4.6 V.

Features

IS61LV6432-6TQ features: (1)Internal self-timed write cycle; (2)Individual Byte Write Control and Global Write; (3)Clock controlled, registered address, data and control; (4)Pentium or linear burst sequence control using MODE input; (5)Three chip enables for simple depth expansion and address pipelining; (6)Common data inputs and data outputs; (7)Power-down control by ZZ input; (8)JEDEC 100-Pin LQFP and PQFP package.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

IS61LV6432-6TQ |

Other |

|

Data Sheet |

Negotiable |

|

||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|

IS61(64)LF12832A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

IS61(64)LF12836A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

IS61(64)LF25618A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

IS61(64)LPS12832A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

IS61(64)LPS12836A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

IS61(64)LPS25618A |

Other |

|

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)